2024. 5. 5. 16:02ㆍCS/Computer Architecture

0. Basic Computer

아래 모든 설명은 Basic Computer를 기준으로 진행한다.

- Basic Computer

: DEC. Corp사의 중형 컴퓨터 PDP-11을 지칭

: 가장 기본적인 컴퓨터 구조

: 현대 CPU와 동일한 설계 구조

1. 명령어 코드 (Instruction Codes)

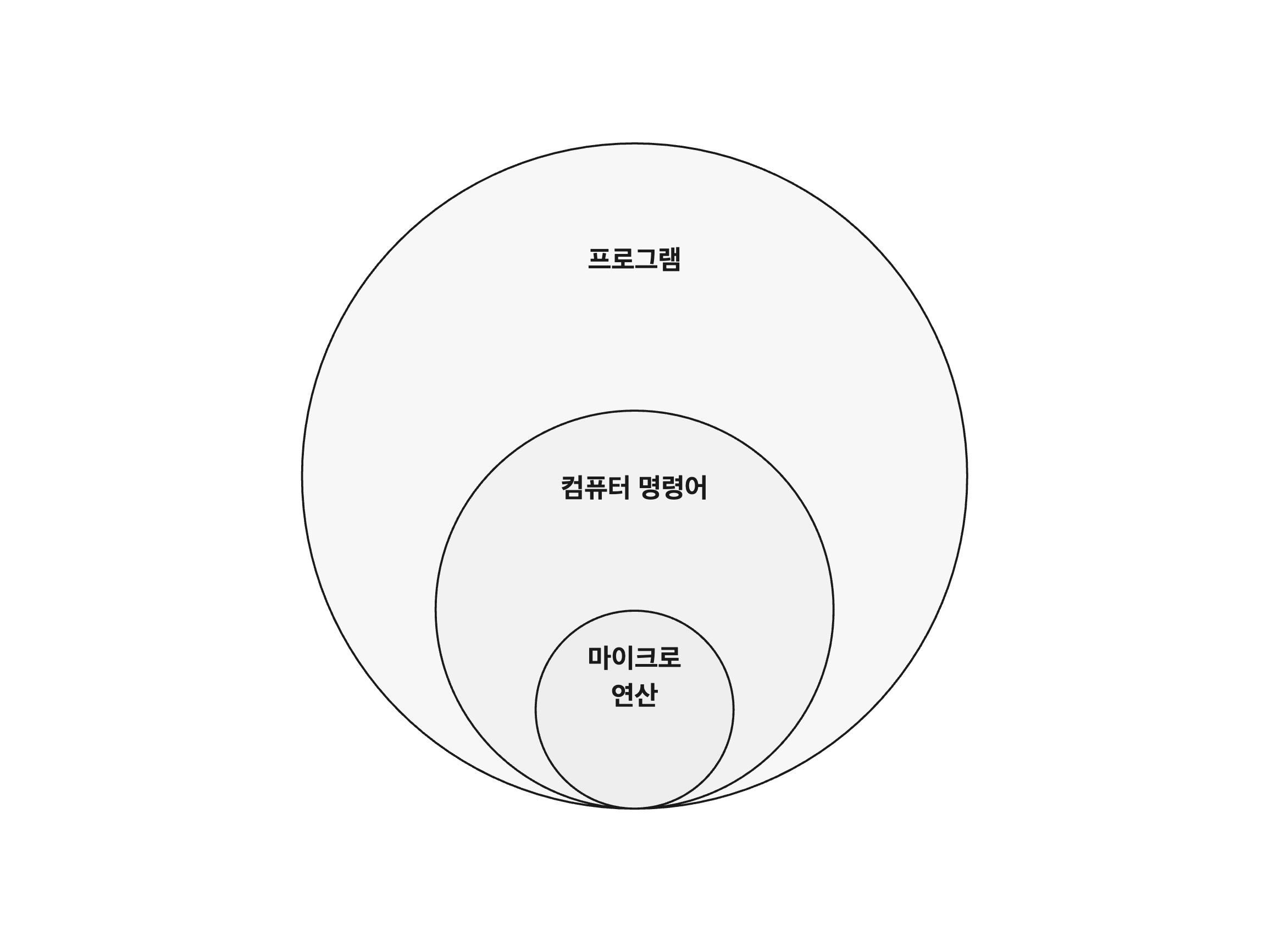

컴퓨터의 동작은 레지스터 내에 저장된 데이터에 대한 마이크로 연산의 시퀀스에 의해 정의된다.

| 항목 | 설명 |

|---|---|

| 프로그램 | 사용자가 원하는 연산과 피연산자가 처리되는 순서를 기술한 컴퓨터 명령어의 집합 |

| 컴퓨터 명령어 | 컴퓨터에 대한 일련의 마이크로 연산을 기술 |

| 마이크로 연산 | 레지스터에 저장된 데이터를 가지고 실행되는 동작. 하나의 클럭 펄스 동안에 실행되는 기본적인 동작. |

여기서 컴퓨터 명령어는 컴퓨터에 대한 일련의 마이크로 연산을 기술하는 이진 코드다.

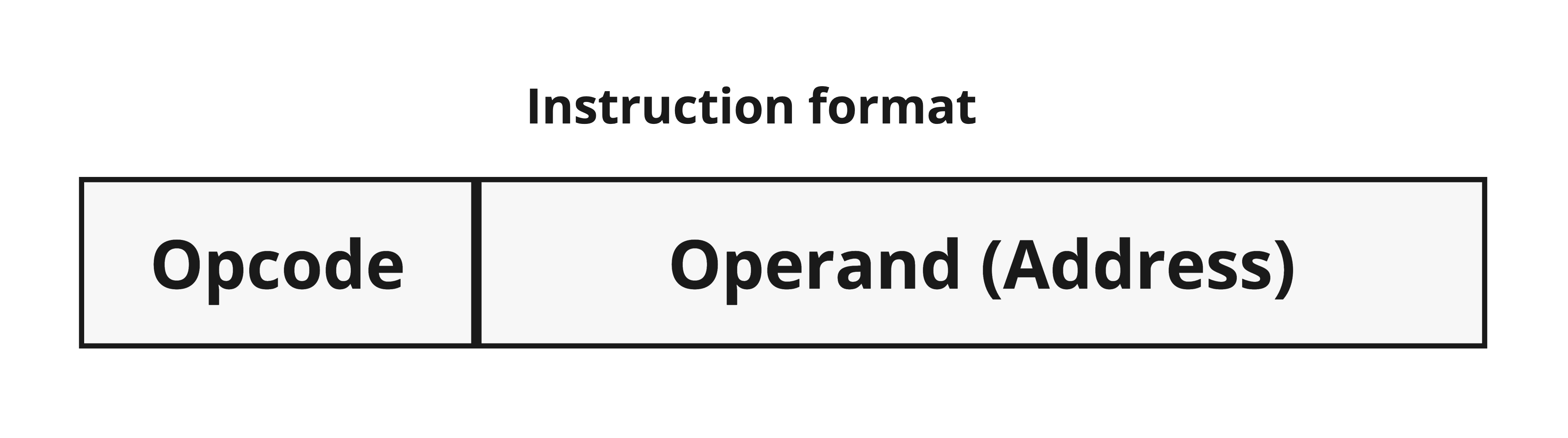

이진 코드는 연산코드와 피연산자로 구성된다.

데이터와 함께 메모리에 저장된다.

- 명령어 코드

: Instruction Code 또는 Operation Code (줄여서 Opcode)

: 컴퓨터에게 어떤 특별한 동작을 수행할 것을 알리는 비트들의 집합.

: 연산 코드들로 구성 (덧셈, 뺄셈, 곱셈, 시프트, 보수 등등)

각 연산 코드를 구현하기 위해서 일련의 마이크로 연산이 발생 → 하나의 연산코드를 매크로 연산이라고 부르기도 한다.

PDP-11의 instruction format이 궁금하다면… 클릭

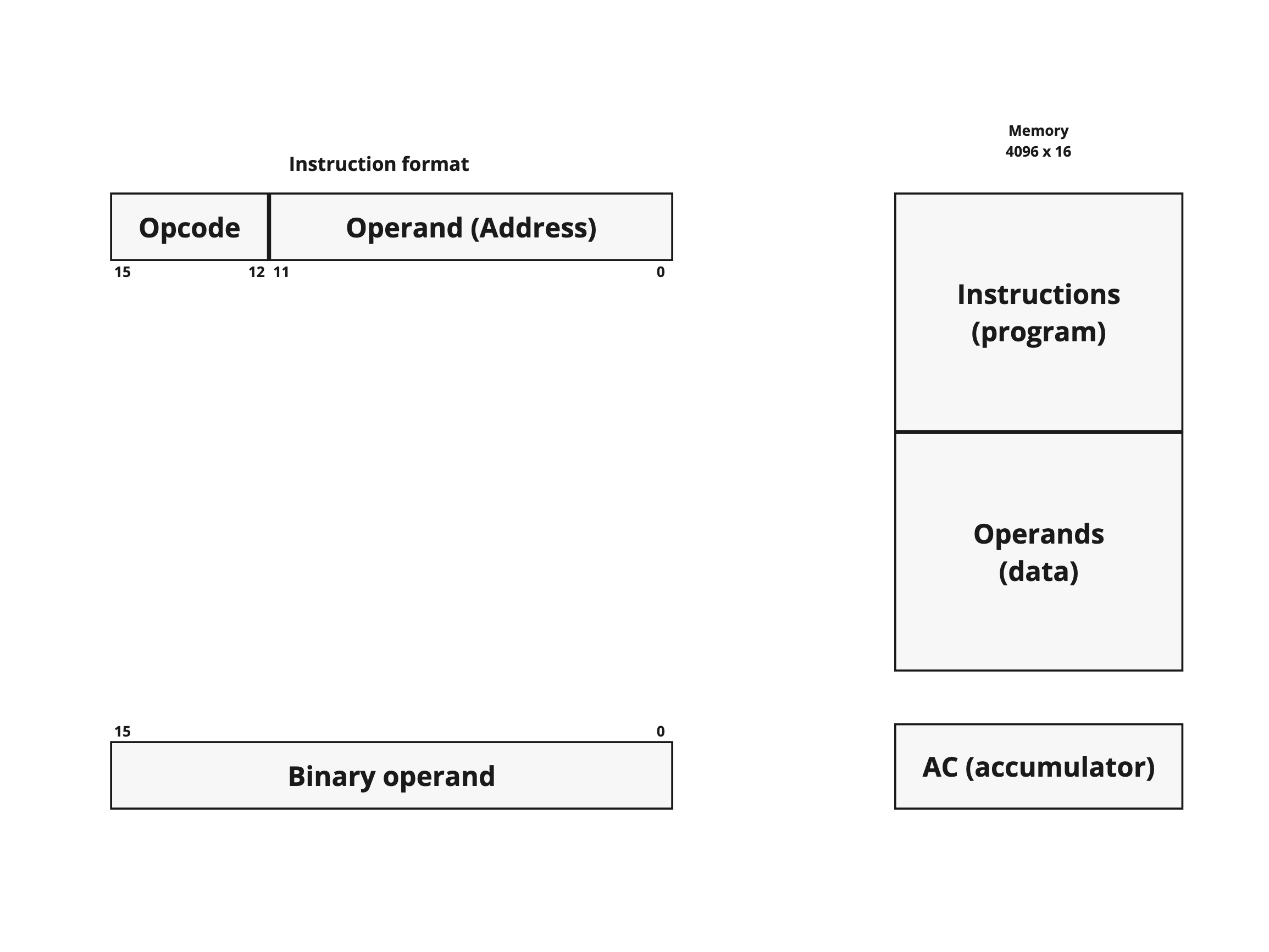

성격에 따라서 메모리의 다른 부분(Segment)에 저장된다. 명령어의 실행 결과는 AC에 저장된다.

(프로그램이 메모리에 저장된다. → 폰 노이만의 프로그램 내장방식을 따른다)

Q. 메모리의 크기는 왜 4096x16일까? 뭘까용?

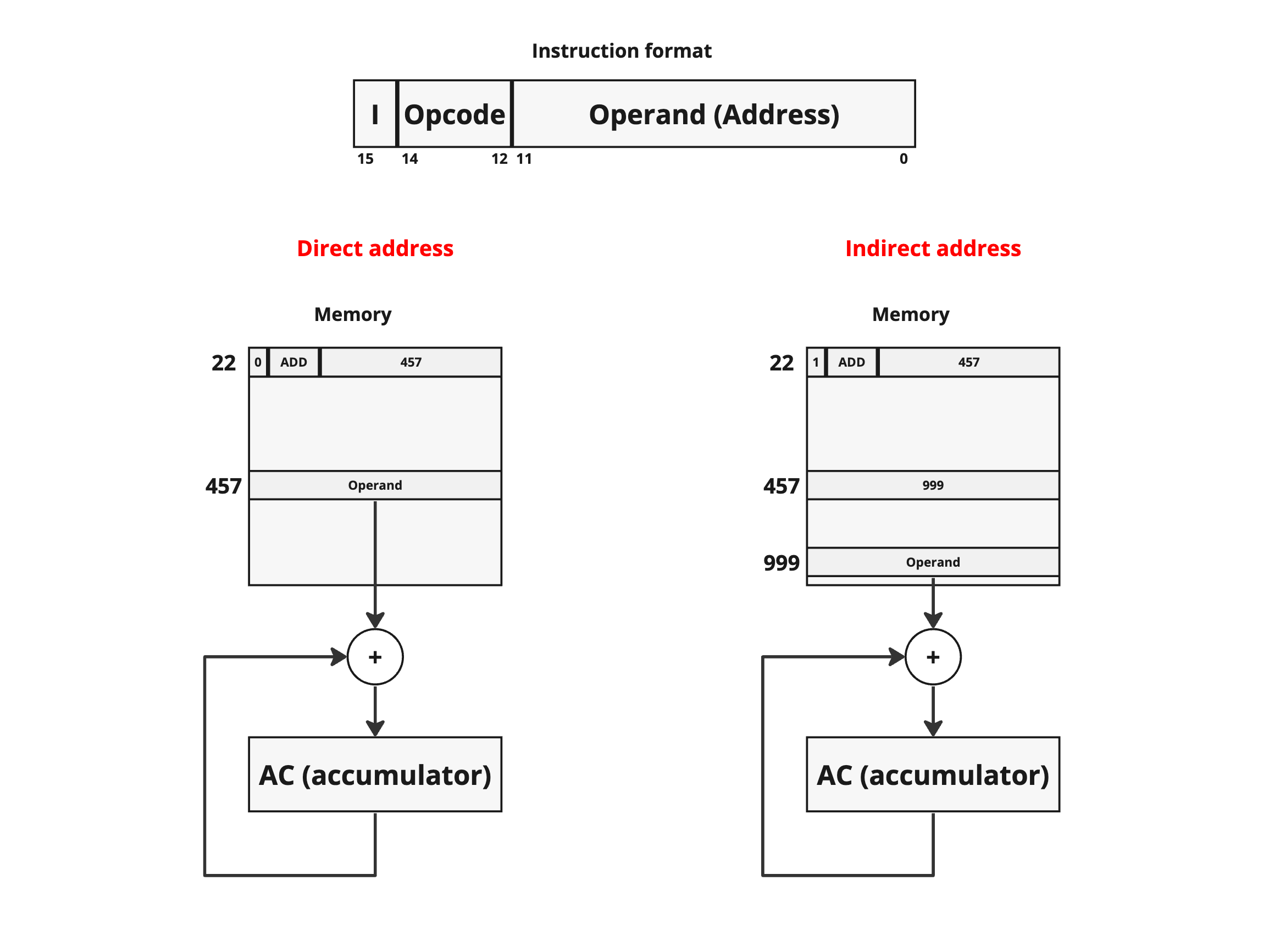

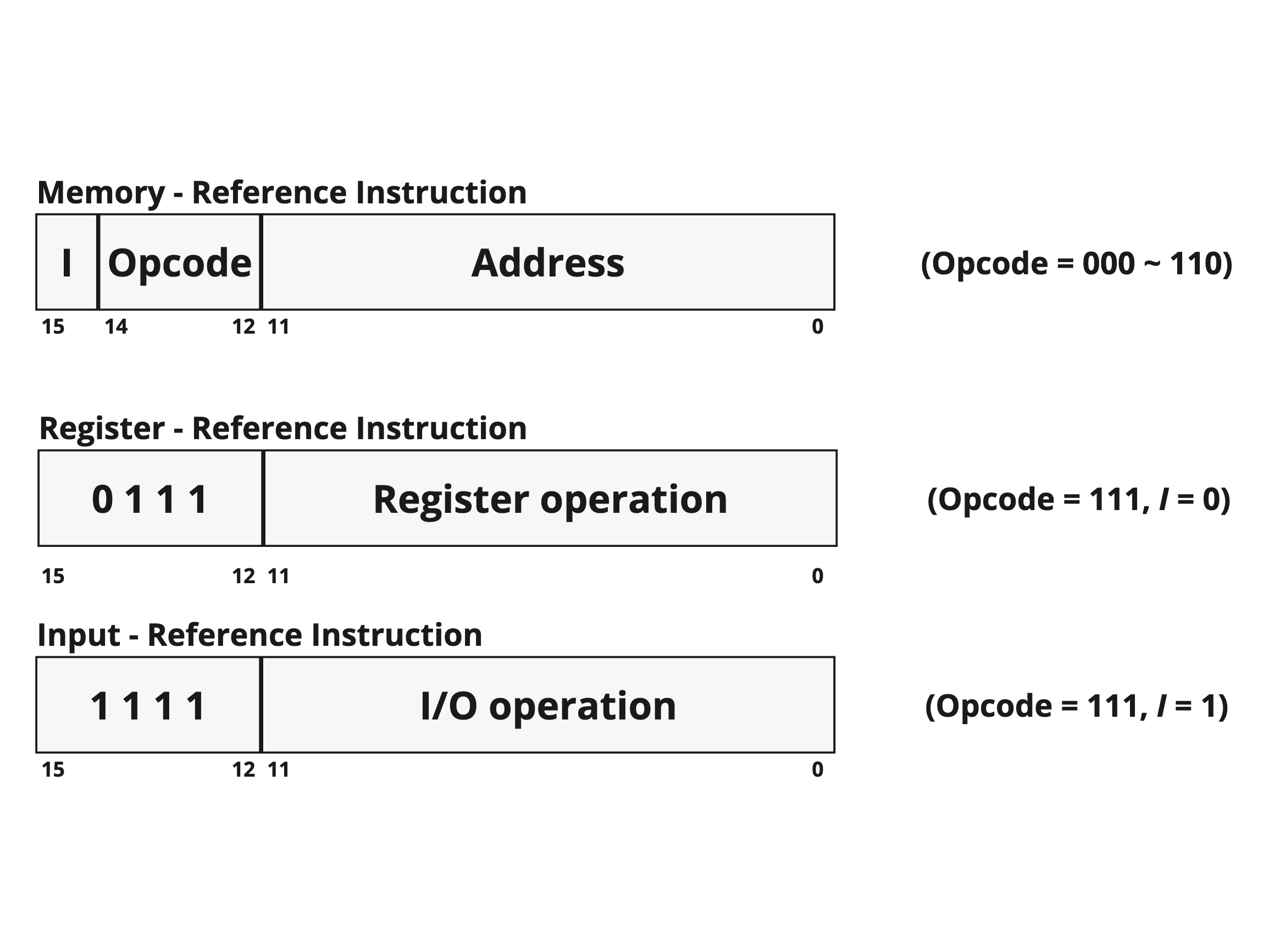

- I bit가

0→ 직접 주소지정 방식 - I bit가

1→ 간점 주소지정 방식

굳이 간접 주소를 사용하는 이유:

- 직접 주소지정 방식은 주소 필드의 길이가 짧기 때문에 주소를 지정할 수 있는 기억장치 범위가 제한된다.

- 프로그래밍 언어의 활용성을 높이기 위해서 필요한 경우가 있음.

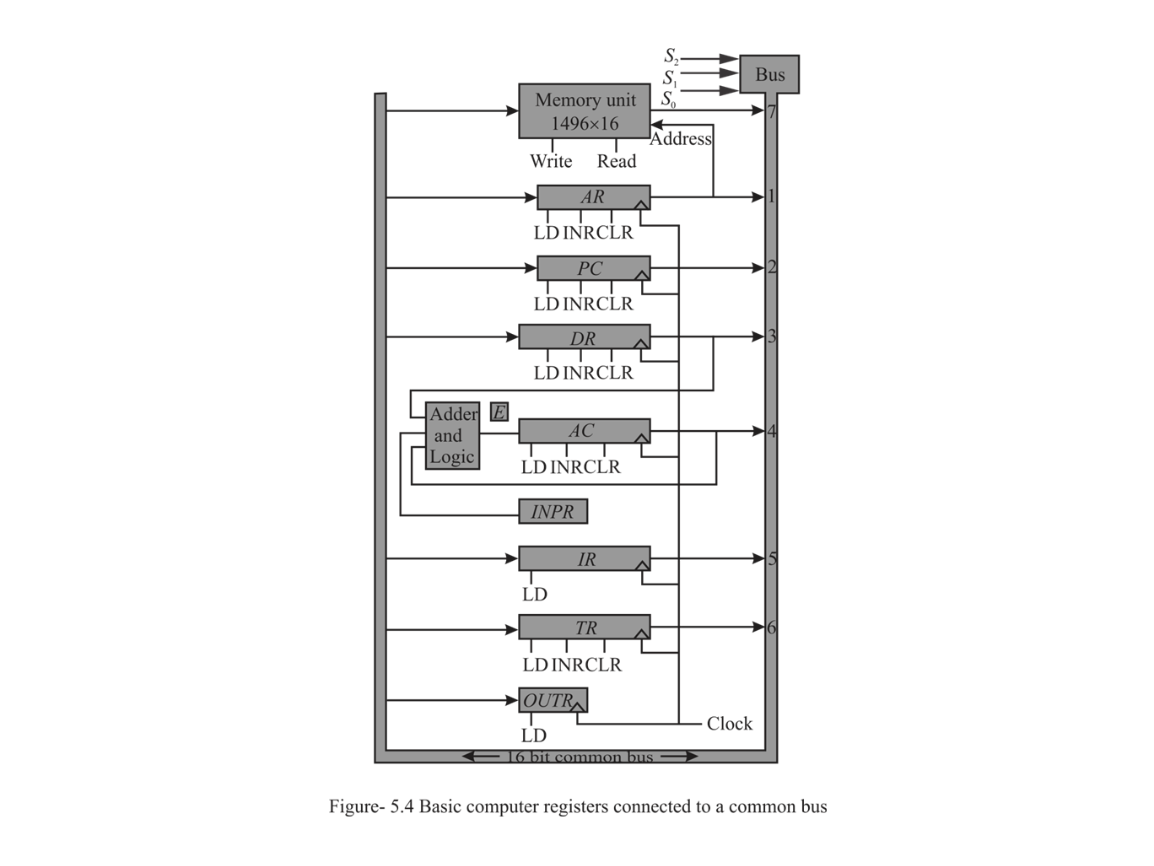

2. 컴퓨터 레지스터 (Computer Registers)

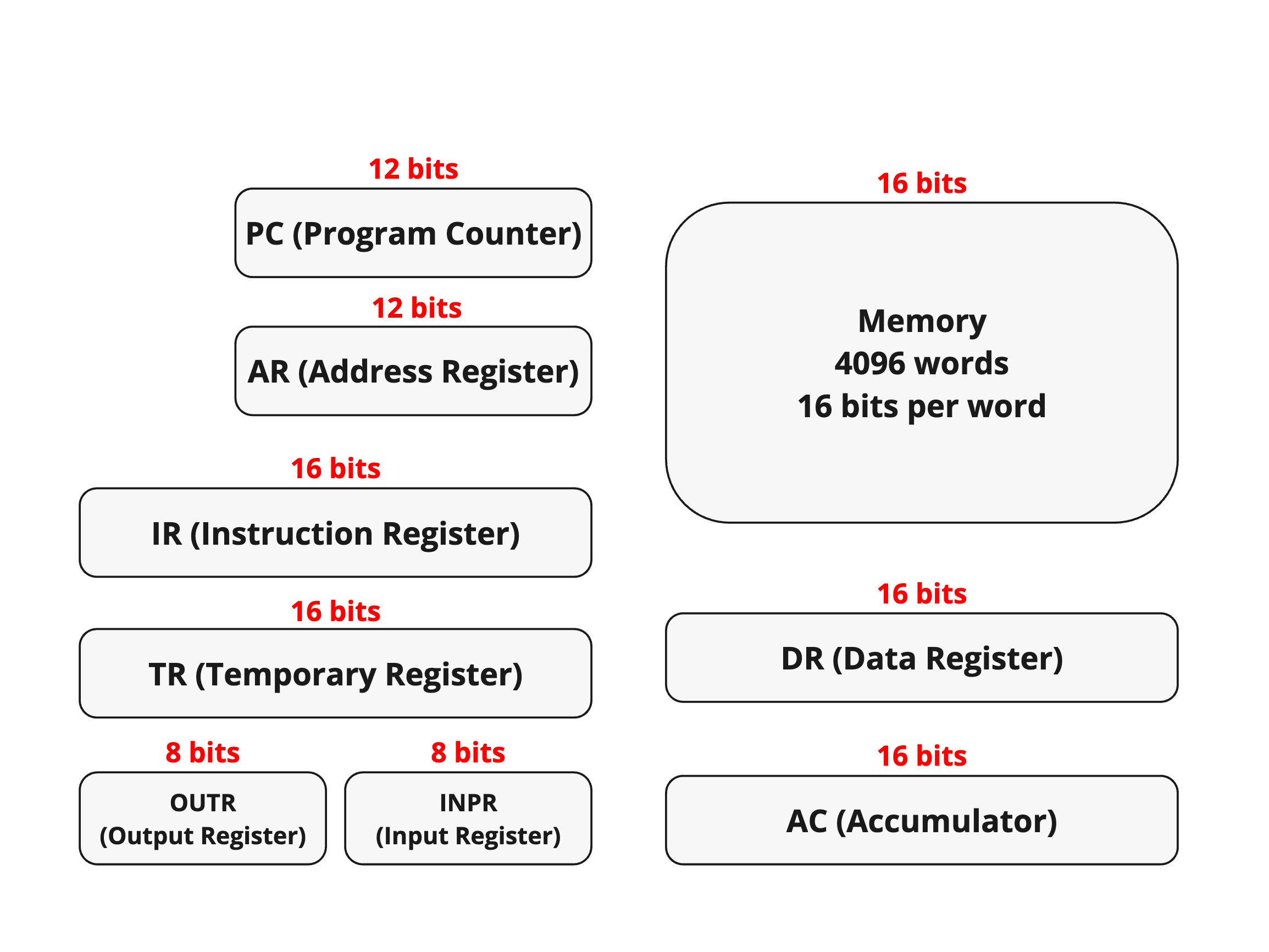

Basic computer를 이루고 있는 레지스터

OUTR와 INPR이 8bits인 이유는 주변 장치들과 8bit 통신을 많이 하기 때문. (지금도 8bit)

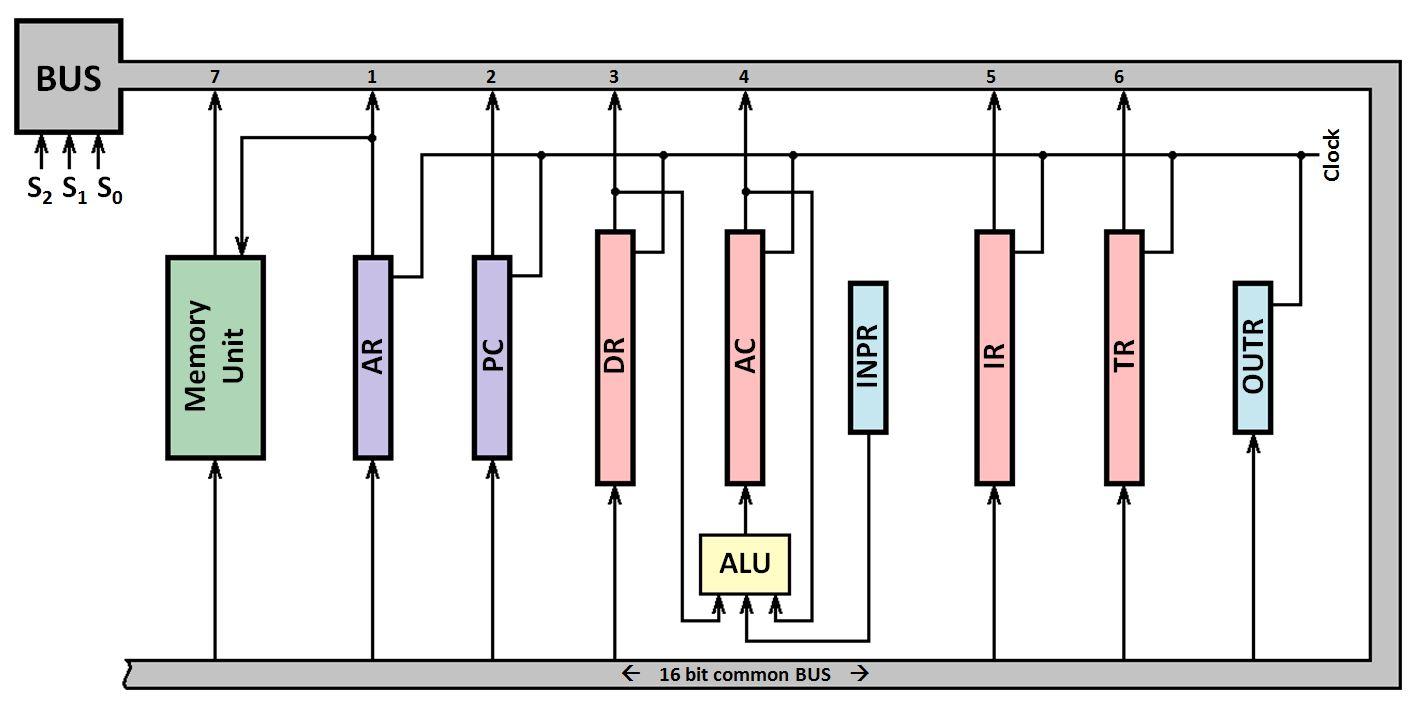

3. 버스

| 버스 종류 | 설명 |

|---|---|

| 내부 버스 (공통 버스) | CPU 내부 레지스터간 연결 |

| 외부 버스 | CPU 내부 레지스터와 메모리간 연결 |

| 입출력 버스 | CPU와 주변 장치 연결 |

공통 버스의 폭으로 CPU word의 크기를 경정.

한 번에는 하나의 신호만이 버스를 사용할 수 있다.

MUX(Multiplexer)가 여러 신호 중 하나의 신호만 골라서 버스에 올린다.

공통 버스와 레지스터들 간의 연결 (https://velog.io/@gyrbs22/전산학-멀티프로세서-시스템)

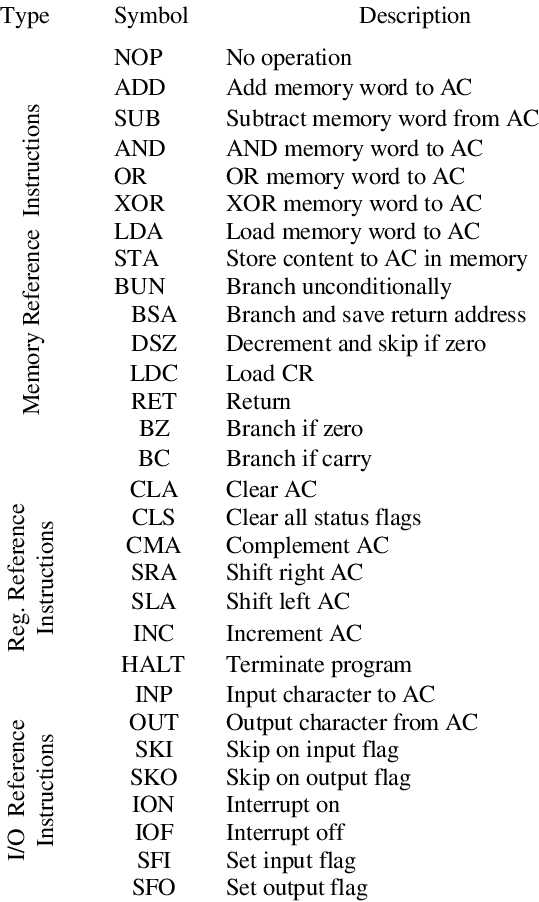

4. 컴퓨터 명령어 (Computer Instructions)

| 기본 컴퓨터 명령어 | 설명 | 개수 | Opcode |

|---|---|---|---|

| MRI | Memory-Reference Instruction. | 7가지 | 000 ~ 110 |

| RRI | Register-Reference Instruction. | 12가지 | 111, I = 0 |

| IO | Input-Output Instruction. | 6가지 | 111, I = 1 |

RRI는 Register operation의 12개 비트를 사용해서 12가지 RRI 중 하나의 Instruction을 선택한다.

IRI도 I/O operation를 사용해서 6가지 IRI 중 하나를 선택.

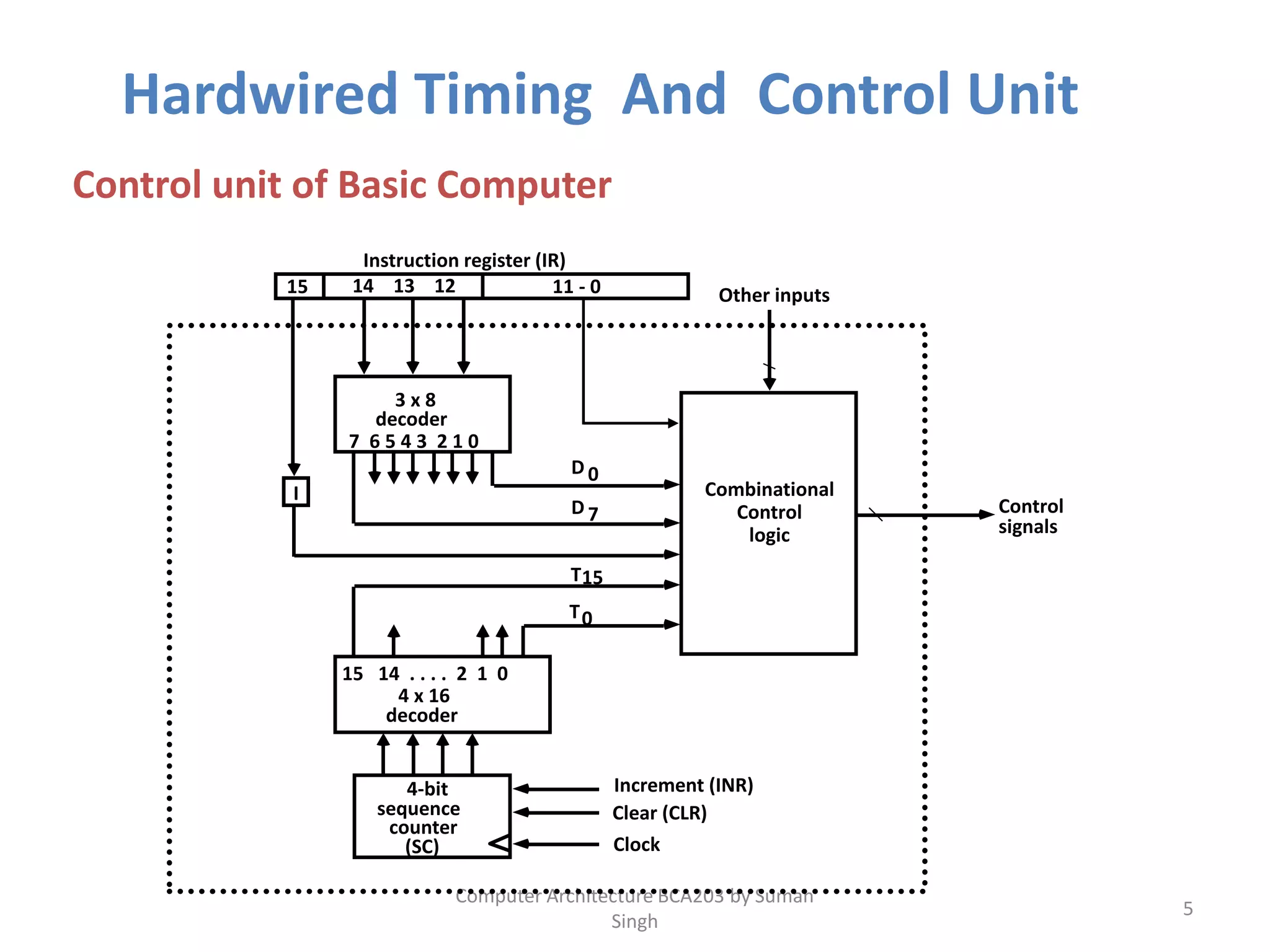

5. 타이밍과 제어 (Timing and Control)

제어 장치(control unit, CU)는 명령어들을 읽고 해석하고, 그것을 실행하기 위한 제어 신호들 (control signals)를 순차적으로 방생하는 하드웨어 모듈이다.

- 명령어 실행에 필요한 각종 정보들의 전송 통로와 방향을 지정하고

- CPU 내부 요소들과 시스템 구성 요소들의 동작 시간(타이밍)도 결정해 준다.

타이밍 신호는 클럭에 의해 생성되며, 클럭은 컴퓨터 내의 모든 동작을 동기화합니다.

(이러한 동작은 명령어 사이클을 통해 실행되며, 각 명령어 사이클은 여러 단계로 나뉘어 있습니다. 아래서 설명)

제어 장치는 구현 방식에 따라 Hardwired Control 방식과 Mirco-programmed Control 방식이 있다.

위의 이미지는 Hardwired Control 방식의 제어 유니트다.

(구체적인 동작 방식에 대해서 알고 싶다면 클릭)

하드웨어로 Instruction을 읽고 해석해서 Control signals를 생성한다.

CPU가 제공하는 명령어들의 수가 많아질수록 제어 유니트의 내부 회로는 더 복잡해진다.

이러한 복잡도를 줄이기 위해서 제어 유니트의 동작을 소프트웨어로 처리하는 방법이 마이크로프로그래밍(Microprogramming)이다.

이 방법을 이용하면 명령어 실행 시간이 느려져서 최근에는 명령어 형식을 단순화하고 하드웨어로 명령어를 실행하는 RISC 설계 개념이 사용되고 있다.

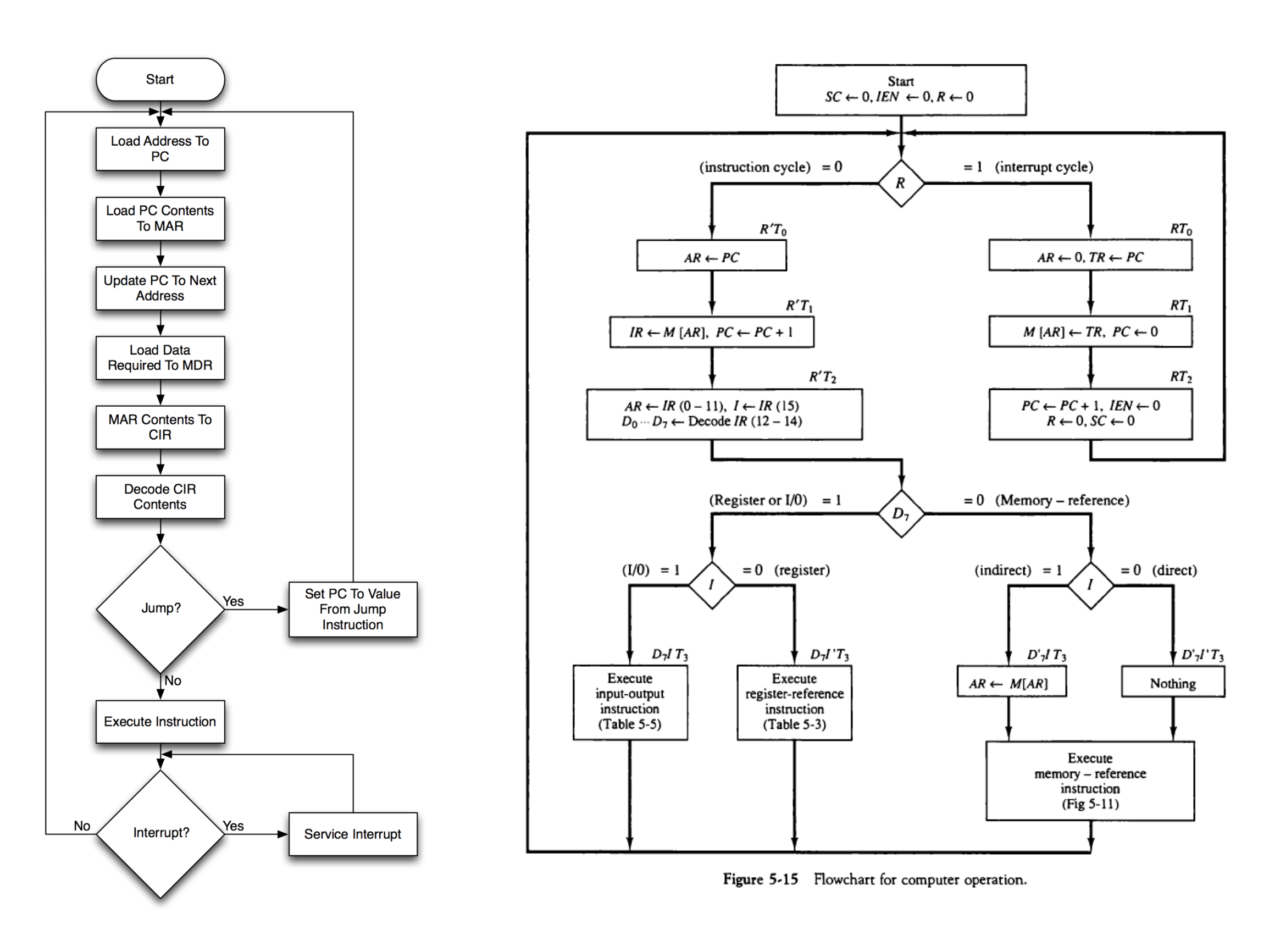

6. 명령어 사이클 (Instruction Cycle)

- 명령어 사이클 : CPU가 한 개의 명령어를 실행하는데 필요한 전체 과정

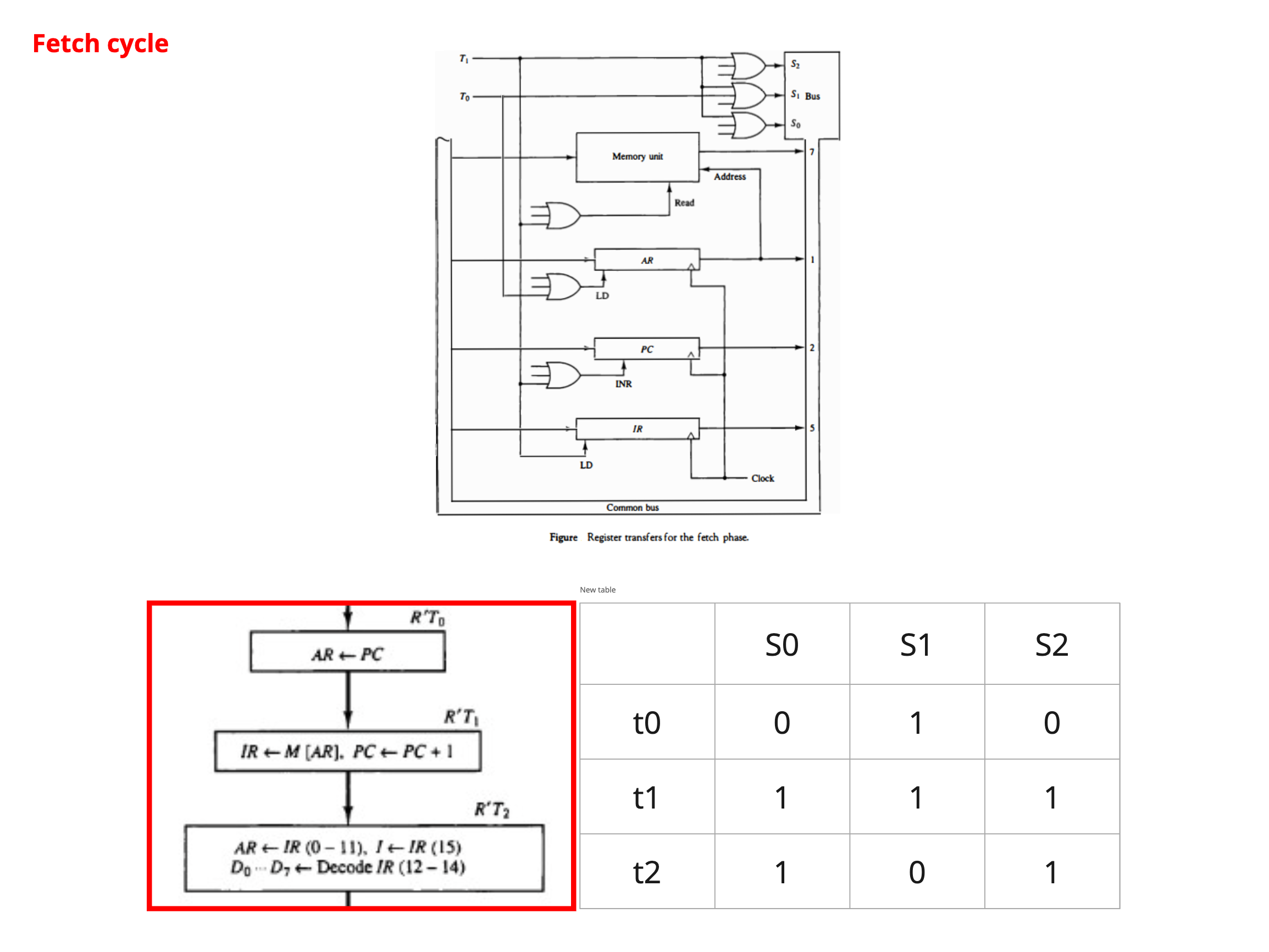

- Fetch cycle

: 프로그램 카운터(PC)가 가리키는 기억장치의 위치로부터 명령어를 인출한다.

: 프로그램 카운터(PC)의 내용을 1 증가시킨다. - Execute cycle

: 인출된 명령어 코드를 해독하고 필요한 연산을 수행한다.- 데이터 이동 : 기억장치, I/O 장치엣 데이터를 가져온다.

- 데이터 처리 : 데이터에 대하여 산술, 논리 연산을 수행한다.

- 데이터 저장 : 연산 결과를 기억장치에 저장한다.

- 프로그램 제어 : PC가 가르키는 위치가 아닌 다른 위치의 명령어 실행. (branch)

- interrupt cycle

: 긴급한 상황에 대한 대처 혹은 외부 장치들과의 상호작용 처리.

D는 3*8 Decoder에서 Opcode를 디코딩한 정보. → 연산코드T는 SC(Sequence Counter)에서 만들어 4*16 Decoder를 거친 정보. → 타이밍

위는 Fetch cycle이 처리되는 과정이고, 각 타이밍에 버스를 제어하기 위한 제어 신호를 의미한다.

각 RRI와 MRI 명령의 동작과정을 알 수 있다.

각 유닛은 동작에 필요한 제어 신호를 추가적으로 수신받는다.

'CS > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조론] 입출력 구조 (0) | 2024.06.21 |

|---|---|

| [컴퓨터구조론] 백터 처리 (2) | 2024.06.21 |

| [컴퓨터구조론] 마이크로-프로그램 (0) | 2024.05.12 |